Notice

The information in this document is subject to change without notice.

COMPAQ COMPUTER CORPORATION SHALL NOT BE LIABLE FOR TECHNICAL OR EDITORIAL ERRORS OR OMISSIONS CONTAINED HEREIN; NOR FOR INCIDENTAL OR CONSEQUENTIAL DAMAGES RESULTING FROM THE FURNISHING, PERFORMANCE, OR USE OF THIS MATERIAL.

This guide contains information protected by copyright. No part of this document may be photocopied or reproduced in any form without prior written consent from Compaq Computer Corporation.

© 1998 Compaq Computer Corporation All rights reserved. Printed in the USA.

COMPAQ, ARMADA, and LTE are registered in the U.S. Patent and Trademark Office.

Microsoft and Windows are registered trademarks of Microsoft Corporation.

The software described in this guide is furnished under a license agreement or nondisclosure agreement. The software may be used or copied only in accordance with the terms of the agreement.

Product names mentioned in this document may be trademarks and /or registered trademarks of their respective companies.

### **Technical Reference Guide**

**Compaq Armada 1700 Family of Personal Computers**

First Edition (July 1998)

Document Number PRT/001A/0698

**Compaq Computer Corporation**

# Contents

# Chapter 1 Introduction

| About This Guide                  | 1 1 |

|-----------------------------------|-----|

|                                   |     |

| Additional Information Sources    |     |

| Notational Conventions            | 1-3 |

| Values                            |     |

| Ranges                            |     |

| Signal Labels                     | 1-3 |

| Register Notation and Usage       |     |

| Bit Notation                      |     |

| Indexed Register Notation         | 1-4 |

| Common Acronyms and Abbreviations |     |

| J                                 |     |

# *Chapter 2* System Overview

| System Architecture       | 2-2 |

|---------------------------|-----|

| Architecture              |     |

| System Memory             | 2-2 |

| Secondary L2 Cache        | 2-2 |

| Shared Flash ROM          | 2-3 |

| System Control            | 2-3 |

| Peripheral Control        | 2-3 |

| Mass Storage              |     |

| Video Graphics Subsystem  | 2-4 |

| PC Card Interface Control | 2-4 |

| I/O Interface             | 2-4 |

| Audio Subsystem           | 2-4 |

| Modem Subsystem           | 2-4 |

| Thermal Management        |     |

| Power Subsystem           |     |

| Power Sources             | 2-5 |

| Power Management          | 2-5 |

| Security                  | 2-5 |

| Intelligent Manageability | 2-6 |

| Expansion Support         |     |

| Specifications            | 2-7 |

|                           |     |

.

.

# Chapter 3 Processor/Cache and System Support

| Processor/Cache Subsystem                |

|------------------------------------------|

| Intel Mobile Pentium II Processor        |

| Cache Memory                             |

| Power Management Support                 |

| PCI Bus Overview                         |

| PCI Bus Addressing                       |

| Option ROM Mapping                       |

| ISA Bus Overview                         |

| Direct Memory Access                     |

| DMA Memory Page Register                 |

| Distributed DMA                          |

| Refresh Operations                       |

| Interrupts                               |

| Nonmaskable Interrupts                   |

| Maskable Interrupts                      |

| Interval Timer                           |

| Real-Time Clock and Configuration Memory |

| BIOS ROM                                 |

| System Identification                    |

| Computer Setup                           |

| Plug and Play (PnP) Support              |

| PC Card Support                          |

| APM Support                              |

| Extended System Configuration Data       |

. .

# *Chapter 4* **System Memory**

| 4-1 |

|-----|

| 4-2 |

|     |

| 4-2 |

|     |

|     |

#### *Chapter 5* **PC Card Interface**

| Functional Description                     |     |

|--------------------------------------------|-----|

| Hardware                                   |     |

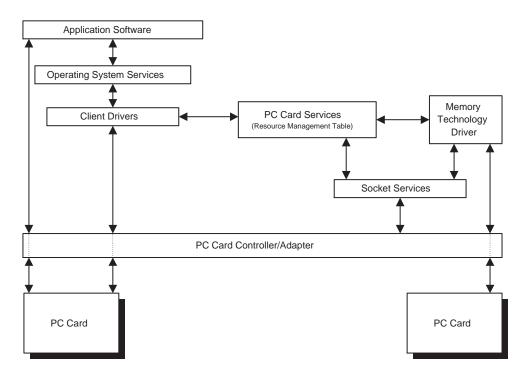

| Software                                   | 5-4 |

| BIOS Initialization                        | 5-5 |

| Operational Overview                       |     |

| Automatic PC Card Detection/Initialization | 5-7 |

| PC Card Interface Operation                | 5-7 |

| 1                                          |     |

# *Chapter 6* Serial, IR Serial, and Parallel Interfaces

| Serial Interface                 | 6-1 |

|----------------------------------|-----|

| Device Registers                 |     |

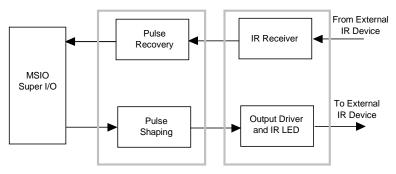

| Infrared Serial Interface        |     |

| Parallel Interface               | 6-7 |

| Standard Parallel Port (SPP)     | 6-8 |

| Enhanced Parallel Port (EPP)     | 6-8 |

| Extended Capabilities Port (ECP) | 6-8 |

| Registers                        | 6-9 |

## *Chapter 7* Audio Subsystem

| Functional Description         | 7-1 |

|--------------------------------|-----|

| Standard Audio I/O             |     |

| Audio I/O                      | 7-3 |

| PCM Operation                  | 7-3 |

| ADC Operation                  |     |

| DAC Operation (PCM)            |     |

| DAC/ADC Configuration          |     |

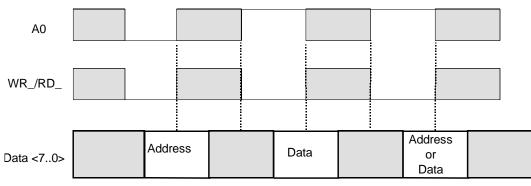

| PCM Bus Cycles.                |     |

| FM Synthesis                   | 7-6 |

| FM Synthesis Cycles            |     |

| Register Programming           |     |

| PCM Registers                  |     |

| FM Synthesis Control Registers |     |

| Audio Subsystem Specifications |     |

|                                |     |

.

-

# *Chapter 8* Graphics/Video Subsystem

| Subsystem Overview           |      |

|------------------------------|------|

| Graphics ASIC                |      |

| Local Bus Interface          |      |

| Memory Interface             |      |

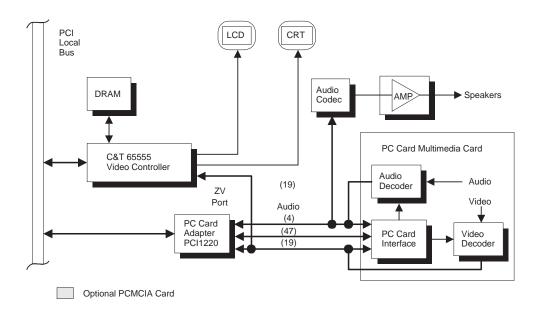

| Attribute Controller         | 8-5  |

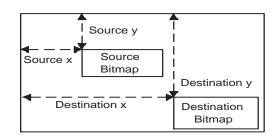

| BitBLT Engine                | 8-6  |

| Color Expansion              | 8-7  |

| Cursor Engine                |      |

| Video Playback               |      |

| RAMDAC                       |      |

| Dithering Engine             | 8-8  |

| CRT Controller               | 8-8  |

| LCD Controller               | 8-8  |

| Power Management             |      |

| CRT Monitor Control          | 8-10 |

| Zoomed Video Port            | 8-11 |

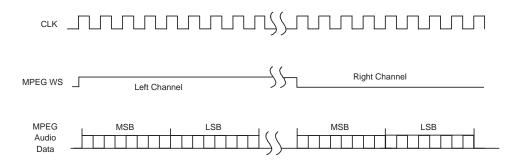

| MPEG-1                       |      |

| MPEG-1 Video Data Structure  |      |

| MPEG-1 Audio Data Structure  |      |

| Liquid Crystal Display (LCD) |      |

| Brightness Control           | 8-15 |

| Display Modes                | 8-16 |

| Text Modes                   | 8-16 |

| Graphics Modes               |      |

| Status Indication            | 8-18 |

. .

# *Chapter 9* Keyboard/Pointing Device Subsystem

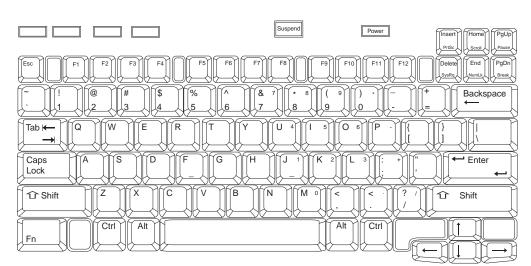

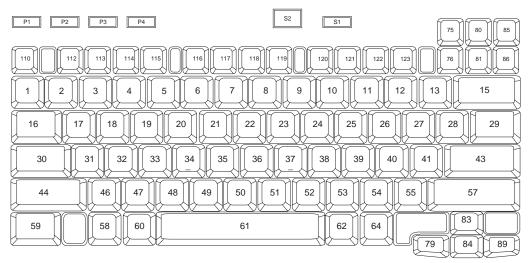

| Internal Keyboard                    |  |

|--------------------------------------|--|

| Keyboard Control                     |  |

| Functional Description               |  |

| Modes of Operation                   |  |

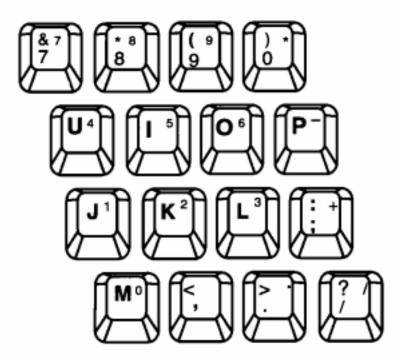

| Num Lock Key                         |  |

| Function (Fn) Key                    |  |

| Embedded Numeric Keypad              |  |

| Cursor- and Screen-Control Functions |  |

| Typematic Function                   |  |

| 51                                   |  |

| Keyboard Scan Modes                    |     |

|----------------------------------------|-----|

| Normal Mode Scan Codes (Scan Set 2)    |     |

| Hotkeys                                |     |

| Pointing Device Interface              |     |

| Pointing Device Initialization         | 9-9 |

| Data Format                            |     |

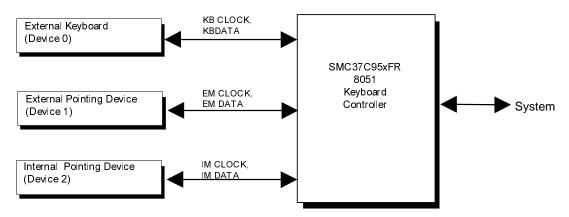

| External Keyboard/Mouse Communications |     |

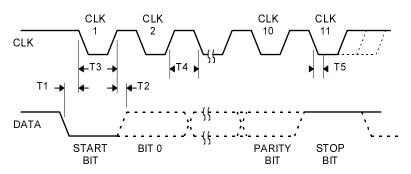

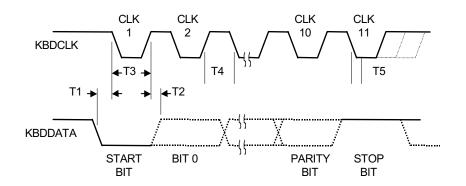

| Keyboard/Mouse-to-System Transmissions |     |

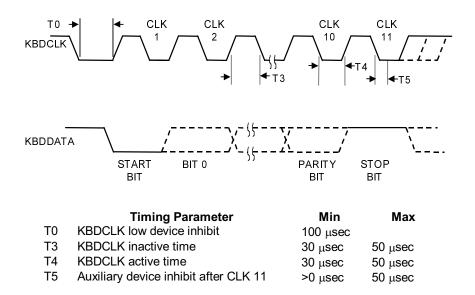

| System-to-Keyboard/Mouse Transmissions |     |

| •                                      |     |

# *Chapter 10* **Power Supply**

| Functional Description                    |  |

|-------------------------------------------|--|

| AC/DC Converter                           |  |

| DC-DC Converter                           |  |

| Fault-Detection Circuits                  |  |

| Battery Pack                              |  |

| Charge Status Monitoring                  |  |

| Master Battery Arbitration                |  |

| Li-Ion Battery Charging/Discharging Order |  |

| Fuel Gauges                               |  |

| RTC Power Supply                          |  |

|                                           |  |

# *Chapter 11* Mass Storage

| Hard Drive Subsystem                | 11-1  |

|-------------------------------------|-------|

| Hard Drive Programming              |       |

| Hard Drive Specifications           |       |

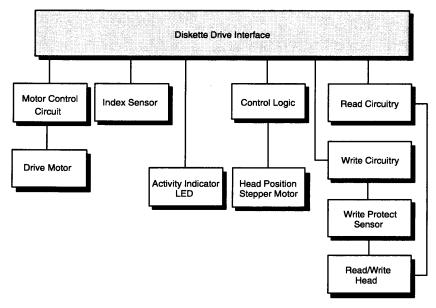

| Diskette Drive Subsystem            |       |

| 1.44-Megabyte Diskette Drive        |       |

| Diskette Drive Controller           |       |

| Diskette Drive Controller Registers |       |

| Drive Controller                    |       |

| Diskette Data Transfer Rate         | 11-8  |

| Write Precompensation               |       |

| LS-120 Drive Subsystem              |       |

| CD-ROM Drive                        |       |

| DVD-ROM Drive                       |       |

| MultiBay 60-Pin Connector           |       |

| Zip Drive                           |       |

| Boot Order                          | 11-15 |

|                                     |       |

# *Chapter 12* Internal Modem

.

.

# Appendix A Error Messages and Codes

| Error Messages                      | A-1 |

|-------------------------------------|-----|

| Common Power-On Messages            |     |

| Initialization Diagnostic Messages  |     |

| Advanced Diagnostics Error Messages |     |

# Appendix B Power Conservation

| Battery Conditions        | B-1  |

|---------------------------|------|

| Operating Mode            |      |

| Power Conservation Levels |      |

| Reduced Power Conditions  | B-6  |

| Local Standby             | B-6  |

| Suspend (Global Standby)  |      |

| Hibernation               |      |

| System Thermal Management | B-13 |

|                           |      |

# Appendix C

# **Security Features**

| Feature Descriptions                                   | C-1 |

|--------------------------------------------------------|-----|

| Power-On Password                                      | C-1 |

| Administrative/Setup Password                          | C-2 |

| QuickLock/QuickBlank                                   | C-2 |

| DriveLock                                              | C-3 |

| Keyboard Lock                                          | C-4 |

| Diskette Drive Protection                              | C-4 |

| Hardware Locks                                         | C-4 |

| Programming Information                                | C-5 |

| Status Read Of Security Features                       | C-5 |

| Status Read Of Security Features Involving Peripherals |     |

|                                                        |     |

Chapter 1

# Introduction

# **About This Guide**

This guide provides technical information on the Compaq Armada 7800 Family of Personal Computers.

### **Additional Information Sources**

Additional information on the products covered in this guide is available from manufacturer's data sheets, application notes, and published industry standards. Please refer to the sources listed below for additional information.

#### **Publications**

For more information on components used in products covered in this guide, refer to the following publications:

- Compaq Computer Corp. and others, Serialized IRQ on the PCI Way, version 5.4.

- Compaq Computer Corp., Compaq BIOS Technical Reference Guide, PN 074A/0693, Third Edition, Copy Date: June 1995.

- Hogan, Thomas, *The Programmers PC Sourcebook*, Microsoft Press, © 1991.

- IEEE, IEEE 1284 Parallel Port Specification.

- Intel Corp., *Mobile Pentium II Processor Data Sheets*.

- Intel Corp., Mobile Pentium Processor with MMX Technology Data Sheets, Copy Date: January 1997, Order No. 243292-001.

- Intel Corp., *Pentium Family User's Manual*, Document No. 241563-003.

- Intel Corp., Pentium Processor Specification Update, Copy Date: May 17, 1995.

- Intel Corporation, Pentium Pro Family Developer's Manual, Intel Corporation, 1996.

- Phillips Semiconductor, I<sup>2</sup>C Peripherals for Microcontrollers Data Book, I<sup>2</sup>C Protocol Reference.

- S3 Inc., S3 Virge\MX<sup>TM</sup> Data Book, Copy Date: July 1996, Document No. DB022-A.

- SMC Corporation, Infrared Communications Controller Specification, revision 1.30, November 1, 1995.

- SMC Corporation, SMC37C957FR Data Sheet.

#### **Online Information**

The following web sites may furnish additional information on products covered in this guide:

- www.compaq.com/support/techpubs/

- www.fapo.com/ieee1284.htm

- www.modems.com/general/mcglossary.html

- www.pc-card.org

- www.picmg.com

- www.s3.com

- www.smc.com

- www.ti.com

# **Notational Conventions**

### Values

I/O addresses and other values are in hexadecimal notation when shown with the letter "h" after them. Memory addresses are in hexadecimal notation when expressed as SSSS:OOOO (SSSS is a 16-bit segment and OOOO is a 16-bit offset). Other references are in binary notation when expressed as ones and zeroes with a trailing letter "b" after the value. All other numbers are in decimal notation.

### Ranges

Ranges or limits for a parameter are shown as a pair of values separated by two dots. For example, 4. .0 includes numbers 4, 0 and every number in between (3, 2, and 1).

## Signal Labels

Signal values are labeled A0, A1, A15, etc. Signal names are in uppercase letters. Signals that are negative true, or active low, are indicated in the text by an underscore (\_) suffix.

# **Register Notation and Usage**

The standard Intel naming conventions are used for the Pentium registers. EAX, EBX, ECX, EDX, EBP, ESP, ESI, and EDI are the names of the general registers used as double word-length registers (32-bit). AH, BH, CH, and DH are the names for the general registers used as high byte-length registers (8-bit); AL, BL, CL, and DL are the names for the general registers used as low byte-length registers (8-bit). SI, DI, and BP denote the source index, destination index, and base pointer registers, respectively.

CS, SS, DS, ES, FS, and GS denote the four segment registers: code segment, stack segment, and four data segments respectively. CS is used with the EIP (instruction pointer) register, and SS is used with the SP (stack pointer) register. EFLAGS is the 32-bit Flag register used to return the status of some operations. Status is given as the state of one of the flags within the register: CF for Carry Flag, IF for Interrupt Flag, etc.

Chapter 2

# **System Overview**

The Compaq Armada 1700 Family models are designed to operate using a 32-bit PCI architecture low-voltage technology, and a 233- or 266-MHz Pentium II processor. Standard features for all models include a keyboard with integrated pointing device and user-programmable keys, a Soundblaster compatible audio board, a modular MultiBay, optical disc bay, battery bay, and plug and play–supported dual 16-/32-bit PC Card slots. Model dependent standard features include a 13.3- or 12.1-inch color TFT XGA or 12.1-inch dual STN display, 32-MB Synchronous Dynamic Access Ram (SDRAM), and a 4.0-GB hard drive. Options include an integrated K56flex modem, a 24X max CD-ROM, and a DVD-ROM drive.

Desktop functionality is provided through the Convenience Base II.

All computer models may be set to operate under DOS, Windows, or other standard operating systems, and are Energy Star compliant. Not all operating systems or operating system versions support all hardware features of this computer

Figure 2-1. Compaq Armada 1700 Personal Computer

# **System Architecture**

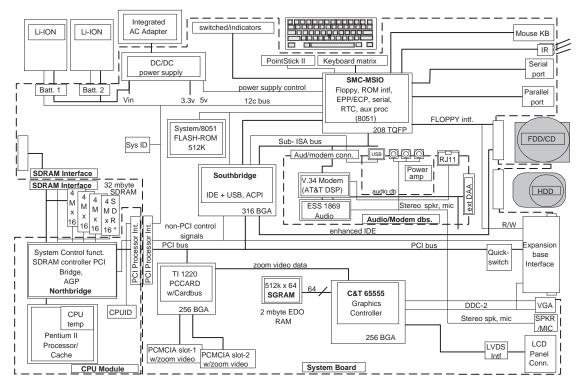

The Computer's system architecture is shown in Figure 2-2.

Figure 2-2. Block Diagram

#### Architecture

The computer architecture is composed of a 64-bit host bus, a 32-bit PCI local bus, and an 8-bit ISA bus. Host, memory, and PCI bus control is accomplished by the Intel 440BX Northbridge and Intel PIIX4E Southbridge. The processor board contains the microprocessor, the L2 cache, 32-MB system memory, and the Intel 440BX Northbridge.

### **System Memory**

The first 32-MB of system memory resides on the system board. The expansion system memory is located on a single SODIMM. The memory is 3.3-VDC, SDRAM operating at host bus speed of 66-MHz.

### **Secondary L2 Cache**

A secondary L2 cache memory system is integrated into the Pentium II processor subassembly. This memory consists of two burst-static-cache RAMS mounted in the processor cartridge.

#### **Shared Flash ROM**

The system flash ROM is capable of being written to, or "flashed," in order to be easily updated by using special BIOS update utility software (ROMPaq). The flash ROM containing the system BIOS code also provides non-volatile storage for the code used by the 8051 controller located in the super I/O device.

#### System Control

The Intel PIIX4E Southbridge contains the PCI to ISA bridge, two 82C59 Interrupt Controllers, the 82C54 timer, the IDE support logic, power management logic, and the USB controller with one USB port.

#### **Peripheral Control**

The SMC37C95xFR MSIO provides the remaining AT compatible 765A Floppy Disk Controller, two 16550A UARTS (one with IrDA encoding/decoding), printer port with extended capabilities including bidirectional high speed, EPP 1.7 and 1.9 modes, ECP mode, PC/AT mode, and PS/2 mode.

The MSIO contains an integrated 8051 microcontroller which provides PS/2 type serial interface ports for the internal pointing device and the external mouse/keyboard connectors. The 8051 also provides key scan circuits to scan the internal keyboard, and provides the system power management functions.

#### **Mass Storage**

The computer is equipped with one factory-installed 4.0-GB hard drive. The hard drive is designed for easy removal and upgrading. The drive type is automatically detected and configured by the system.

The diskette drive controller supports 3.5-inch,1.44-MB diskette drives. The diskette drive is provided as a standard MultiBay module. The MultiBay will also accept optional LS-120 diskette drive, Zip drive, a second battery pack or second hard drive. The optical disc bay is a dedicated bay that accepts a 5.25-inch, 24X max CD-ROM or DVD drive.

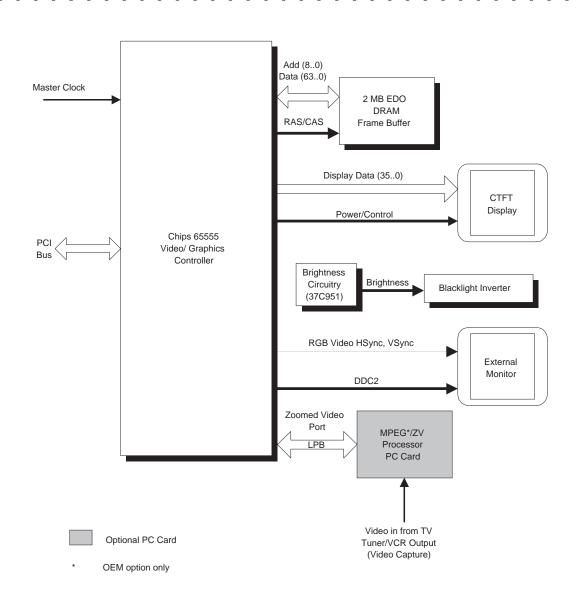

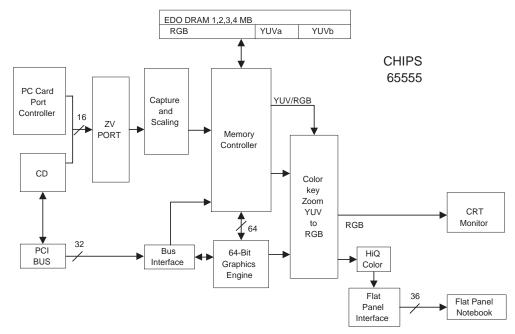

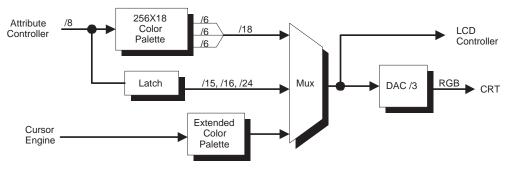

### **Video Graphics Subsystem**

The video graphics subsystem consists of the C&T 65555 video graphics controller interfaced to the processor via the 33- MHz PCI bus, 2-MB of memory, and a 13.3-or 12.1-inch color TFT or 12.1 inch dual STN LCD. In addition to the integrated LCD panel, the graphics controller can also support either the Energy Star Monitor, Reduced Emissions Video Graphics Color Monitor, Video Graphics Color Monitor, or the Video Graphics Monochrome Monitor. Multimedia capabilities are provided by the C&T 65555<sup>TM</sup> video controller through a 16-bit Zoomed Video port.

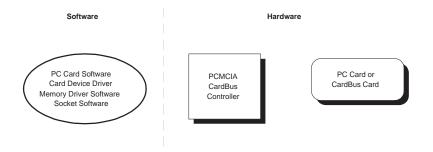

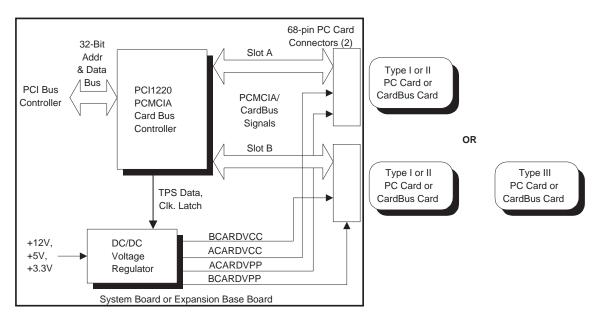

#### **PC Card Interface Control**

Models provide two slots for installing either two Type I or Type II PC Cards, or one Type III PC Card. A single device controls the operation of two 32-bit, multiplexed, synchronous PC Card slots. The PC Card interface supports 3-v and/or 5-v PC Cards in a keyed socket that conforms to the PC Card Standard version 5.0. Both CardBus PC Card (32-bit mode) and 16-bit PC Card modes are supported to allow for bus mastering (32-bit mode) and Compaq PC Card DMA support (16-bit PC Card legacy mode) for peripheral devices such as memory or communications devices. The plug and play feature allows 16-bit PC Card(s) or CardBus PC Card(s) to be plugged into the system without powering down, reconfiguring, or rebooting the system.

#### I/O Interface

The I/O interface used in the includes a serial interface, a serial infrared interface, a parallel interface, and a Universal Serial Bus (USB) interface. These ports are configurable as COM1, COM2, COM3, or COM4, and LPT1, LPT2, and LPT3.

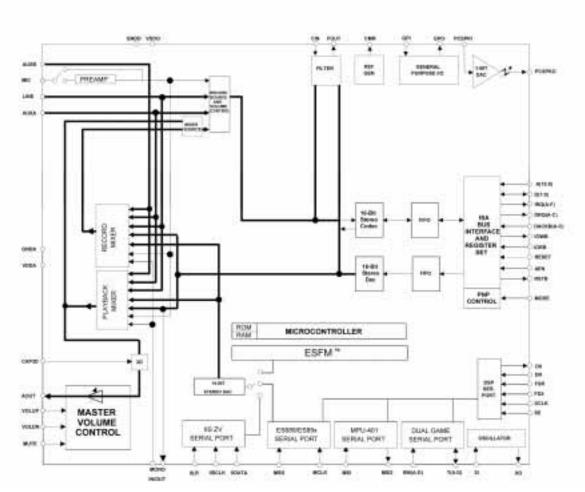

#### **Audio Subsystem**

The audio is derived from an ESS1869 audio controller, a TPA-0102 amplifier, and equalization circuitry. The audio subsystem is fully compatible with industry standard sound cards and the Microsoft Windows Sound System.

#### **Modem Subsystem**

The internal data/fax modem also provides RJ-11 and international DAA connectivity. The modem is a controllerless design capable of 56kbps.

#### **Thermal Management**

Thermal Management is implemented by a CPU temperature-control system that regulates the processor temperature through a temperature-controlled fan, a heat dissipating heat sink, processor clock modulation, and power management.

#### **Power Subsystem**

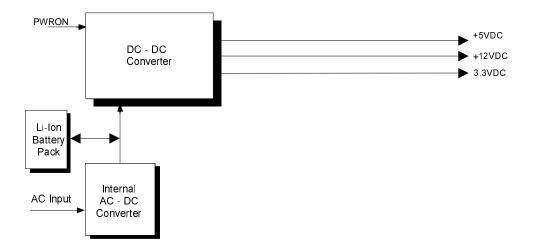

The power subsystem for the computer is made up of the following components:

- Internal AC/DC converter

- DC/DC converter providing outputs of:

+3.3 V (4.0 A), +5 V (5.0 A), +12 V (0.075 A)

- Display inverter to generate high voltage for CCFL backlight.

- Power management controller

#### **Power Sources**

The computer derives power from the following power sources:

- Smart Li-Ion battery pack(s)

- AC from standard AC power lines

- Automobile/Aircraft adapter charger

#### **Power Management**

The power management feature allows the system to enter several levels of reduced power consumption initiated by the user through the keyboard or automatically during periods of reduced activity. Power Management is provided in both AC and DC power modes. Both Advanced Power Management (APM) and Advanced Configuration and Power Management (ACPI) are supported.

#### Security

The computer is protected against unauthorized access through user-selected password entry requirements and disabling techniques. Cable Lock and other hardware-locking provisions are available to prevent unauthorized removal of the computer, expansion/convenience bases, and/or devices.

Security is enhanced through additional password requirements for access to the computer or network and through device disabling for hard drives and I/O ports.

#### **Intelligent Manageability**

Insight Management Agents Version 3.51 is preinstalled. This version does include notification of battery charge faults and failures and external monitor fault alerts. This version is not Desktop Management Interface (DMI) 2.0 compliant.

Compaq will release an updated version of the Insight Management Agents that includes these new features. When available, this updated version will be available on the *Compaq Support Software CD*, or may be downloaded from the Compaq Web site at www.compaq.com/support/files.

NOTE: The installed version of the Insight Management Agents is DMI 2.0 compliant.

The version of Insight Management Agents installed on the Computer provides fault management capabilities that issue alert messages to notify the user of any impending hardware failures. Local and network alert notifications are displayed for SMART hard drive failures, memory changes, and system overheating. The Insight Management Agents also work with Compaq Insight Manager and other management applications used to remotely manage computers connected to a network.

For additional information on Intelligent Manageability please check out the following sources:

- Online information:

- compaq.com: http://www.compaq.com/im/index.html

- Agent availability:

- Downloads: http://www.compaq.com/support/files

- □ Support Software CD

#### **Expansion Support**

The main system unit of the computer can be connected to the Convenience Base II for desktop functionality and expandability. The system unit can be used as a network-ready desktop system when connected to the convenience base . The convenience base provides a permanent desktop base for the system unit and eliminates device connection/disconnection problems. Connection to an external CRT and full-size keyboard and mouse are also provided, along with MIDI/joystick, stereo speakers, and port replication.

# **Specifications**

| Table 2-1<br>Computer Specifications       |                               |                     |

|--------------------------------------------|-------------------------------|---------------------|

|                                            | U.S.                          | Metric              |

| Dimensions                                 |                               |                     |

| Height                                     | 2.3 in                        | 5.84 cm             |

| Depth<br>Width                             | 9.6 in<br>12.5 in             | 24.5 cm<br>31.75 cm |

|                                            | 12.3 11                       | 31.73 UII           |

| Weight<br>With battery and optional CD-ROM | 8.3 lbs                       | 2 55 kg             |

| Standalone (Battery) Power Requirements    | 0.3 105                       | 3.55 kg             |

| Nominal Operating Voltage (Li-lon)         | 14.2                          | 14.2                |

| Nominal Operating Voltage (Li-1017)        | 9.6                           | 9.6                 |

|                                            | 9.0<br>45 W                   | 9.0<br>45 W         |

| Maximum Operating Power                    |                               |                     |

| Peak Operating Power                       | 50 W                          | 50 W                |

| Integrated AC Power Power Requirements     |                               |                     |

| Operating Voltage                          | 100 to 240 VAC RMS            | 100 to 240 VAC RMS  |

| Operating Current                          | 1.1 A RNS                     | 1.1 A RMS           |

| Operating Frequency Range                  | 47 to 63 Hz AC                | 47 to 63 Hz AC      |

| Maximum Transient                          | 4/50 kV                       | 4/50 kV             |

| Temperature                                |                               |                     |

| Operating                                  | 5 to 95°F                     | 10 to 35°C          |

| Nonoperating                               | -4 to 140°F                   | -30 to 60°C         |

| Relative Humidity (noncondensing)          |                               |                     |

| Operating                                  | 10 to 90%                     | 10 to 90%           |

| Nonoperating ( $t_W = 38.7^{\circ}C$ max)  | 5 to 90%                      | 5 to 90%            |

| Altitude                                   |                               |                     |

| Operating                                  | 0 to 10,000 ft                | 0 to 3.15 km        |

| Nonoperating                               | 0 to 30,000 ft                | 0 to 10.14 km       |

| Shock                                      |                               |                     |

| Operating                                  | 10 G, 11 ms, half sine        |                     |

| Non operating                              | 240 G, 2 ms, half sine        |                     |

| Vibration                                  |                               |                     |

| Operating                                  | 0.55 G, 0.25 Oct/Min swe      | ep rate             |

| Nonoperating                               | 1.5 G, 0.5 Oct/Min sweep rate |                     |

**NOTE:** Applicable product safety standards specify thermal limits for plastic surfaces. The Compaq Armada operates well within this range of temperatures.

Chapter 3

# Processor/Cache and System Support

# Int*r*od*u*ct*i*on

This chapter briefly describes the Mobile Pentium II processor (MP2) and two ASICs used on the Compaq Armada 7800 Family of Personal Computers. The ASICs include the Compaq Northbridge and Compaq Southbridge.

The computer system supports interchangeable CPU modules that plug into the CPU interposer board. The core logic on the CPU interposer board translates the processor bus interface into a PCI interface, an Accelerated Graphics Processor (AGP) interface, and a 64-bit DRAM interface to the system board.

This chapter describes the system processor, bus architecture, and system support consisting of the following devices:

- Processor/cache subsystem

- AGP bus overview

- PCI bus overview

- ISA bus overview

- Direct memory access

- Interrupts

- Interval timer

- RTC and configuration memory

- BIOS ROM

- System I/O map

P*r*oc*e*sso*r*/Cach*e* S*u*bsyst*e*m

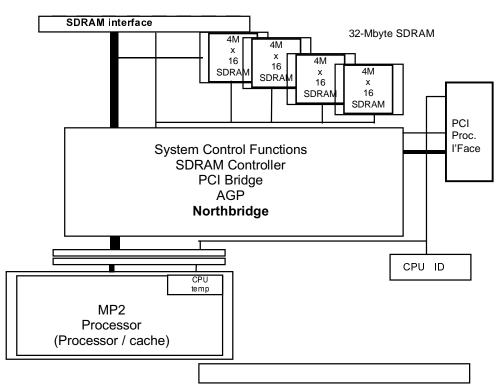

The computer is built with an MP2 and two Compaq ASICs—the Northbridge and Southbridge—that integrate a number of bus control and memory functions on the processor board. Refer to Figure 3-1 for a block diagram of the processor board.

Figure 3-1. Processor/Cache Subsystem Board, Block Diagram

The mobile Pentium II processor is supplied as an integrated subassembly containing the processor, 512-KB L2 cache, and an integral processor temperature sensor. The module is supplied in a shielded cartridge with integral 240-pin Berg connector, providing a high-speed data bus interface to the system.

# Mob*ile* Pentium II Processor

The Mobile Pentium II (MP2) processor is object code compatible with software written for Intel 8086/88, 80286, 80386/486 DX/SX, 486 DX2, Pentium, and Pentium II processors. The MP2 processor has all the features of the Pentium II processor, plus voltage reduction technology and improvements in architectural design and other enhancements to provide substantially greater performance for graphics, video, and audio. The MP2 adds an integral L2 cache to the processor module for higher performance. A temperature monitor permits better thermal management in demanding environments.

Features provided by the mobile Pentium II processor include:

- Enhanced Pipelined Floating-Point Unit

- MMX technology

- Write-back MESI protocol for cache data

- Internal parity checking

- Execution checking

- Performance monitoring

- System Management mode

- Virtual mode extensions

- Fully compatible with MS-DOS, Windows, OS/2, and UNIX operating systems

New features provided by the mobile Pentium II processor include:

- Multiple Branch Prediction

- Past history

- Typical usage

- Reduced voltage technology

- 1.8-, 2.0-, and 2.5-volt core voltage

- 3.3-volt Vcc

- Separate internal 16-KB data and 16-KB instruction caches

- Superscalar architecture with:

- Enhanced 12-stage pipeline

- Two pipelined integer units capable of four instructions/clock

- Pipelined MMX unit

- Pipelined floating-point unit

- Advanced design features:

- Pool of four write buffers used by both pipelines

- Enhanced branch prediction

- Virtual mode extensions

- On-chip module power-down capabilities for extended battery life

- Core frequency of 266-MHz at 66-MHz bus frequency

- Dual Independent Bus architecture

- Processor to main memory bus

- Processor to L2 cache bus

- Integral L2 cache

- Integral CPU Temperature monitor

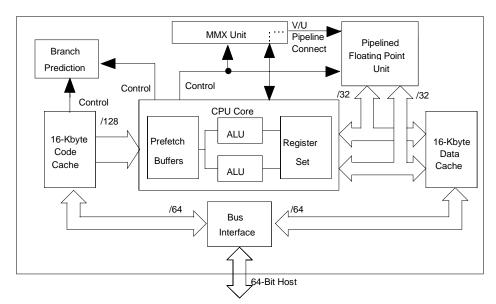

Figure 3-2. Mobile Pentium II Processor, Block Diagram

The mobile Pentium II processor provides a 64-bit external data bus with the ability to pipeline all reads and a number of writes. The system memory interface architecture complements the microprocessor by reducing the number of wait states by the number of clocks pipelined for a given cycle.

The mobile Pentium II processor contains a 32-KB Level 1 (L1) cache. This cache is divided into 16-KB for code and 16-KB for data. The data cache is designed as a write-back cache, which means that data written from the CPU can be retained in the primary cache without being immediately passed on to the secondary cache or system memory, thus providing the CPU with a quicker turnaround in processing. The secondary cache and/or system memory is updated later when it is more convenient for the bus to handle the transfer.

Dual 12-staged pipelined architecture using dual-ALU operation provides 4 instructions-per-cycle performance. The prefetch buffer can hold more than 1 instruction and partially decodes 2 instructions at a time to determine if they can be processed in parallel.

If the two instructions are not reliant upon each other and meet other criteria, they are each routed simultaneously to a processing pipeline. Final decoding is completed, and the instructions are executed in the ALUs. The data cache is arranged as a two-way setassociative cache, so each way can service an ALU simultaneously if the two requested data are in different ways. Once an instruction completes a stage in the pipeline, that stage is free to accept another instruction. CPU Mod*e*s

The Pentium II processor uses a CPU core that is compatible with software written for x86/88 microprocessors. The CPU core can operate in real, protected, or virtual mode. The microprocessors used in this system also support clock control and system management mode (SMM), during which power conservation operations are performed. The SM mode is discussed in the CPU Power Management Support subsection.

### Cach*e* M*e*mo*r*y

The system uses a two-level (L1 and L2) cache system. The Pentium II processor includes 32-KBs of first-level (L1) cache memory that is divided into 16-KB halves. One half is designated as a code (instruction) cache, and the other half is designated for data. Each half operates as a two-way set-associative cache based on the modified/exclusive/shared/invalid (MESI) cache consistency protocol.

- Modified state: Indicates that the cache content of the indicated address is valid and has been written to more than once by the CPU. For a write-back cache, this means the cache contains the only valid data for this location, and the system memory contains obsolete data for that location.

- Exclusive state: Indicates that the CPU (L1) cache contains an exclusive copy of a location in system memory.

- Shared state: Indicates that both L1 and L2 caches contain copies of a location in system memory.

- Invalid state: Indicates that the current cache location contains obsolete data and should not be used.

If one cache has a modified or exclusive line, all matching lines in the other cache will be marked as invalid.

The code cache portion of the L1 cache is write-protected to prevent code from being inadvertently corrupted and supports the shared and invalid states of MESI. The data cache portion of the L1 cache supports all four MESI states.

The second-level (L2) cache memory includes 512 KB of two-way set-associative synchronous SRAM that works independently of the L1 cache and supports write-back operation. The L2 cache is located in the processor module.

#### Power Management Support

Mobile Pentium II processors support a system management mode (SMM) that is utilized by power management firmware to conserve power consumption and extend battery life. The SMM support package includes the following elements:

- System management interrupt (SMI), which is non-maskable and has the highest priority (even over the NMI). The SMI is delivered through the SMI pin only; APIC operation is not supported on this system.

- System management memory (SMRAM), which holds the SMI handler code and CPU state data. A status signal, SMIACT\_, is provided to facilitate access to the SMRAM.

- Resume (RSM) instruction for exiting the SMM.

- I/O Restart and Auto Halt Restart features.

The SMM is initiated by an action that generates the SMI interrupt, which results in the following sequence:

- 1. The CPU asserts the SMIACT\_ signal while in SMM to enable the SMRAM.

- 2. The CPU saves its state to SMRAM starting at base address 3FFFFh and works down as in a stack.

- 3. The CPU switches to SMM, which equates to real mode in the following areas:

- a. Address calculation

- b. GB limit checking

- c. Clearing of IF, TF, and DR7

- d. NMI disabling

- e. RSM instruction opcode becomes valid

- 4. The CPU jumps to the absolute address of 38000h in SMRAM to execute the SMI handler code and perform system management activities.

- 5. At its completion, the SMI handler executes the RSM instruction, which restores the CPU state from SMRAM, deasserts the SMIACT\_ signal, and returns control to the previously interrupted program.

The chipset supports power management features similar to the Intel SL chip set. The most important features are the six programmable I/O break and activity timers that allow idle peripherals to be shut down. The controller uses the SMI interrupt to signal the microprocessor that the timeout has occurred. The ability to reduce the speed of the microprocessor when maximum power is not required is provided by the controller. The speed reduction is accomplished by generating a stop clock event. The duration of the event is programmable. The SMI handler is in a protected region of the ROM and operates independently of the operating system.

For further information concerning the mobile Pentium II processor, refer to *Mobile Pentium II Processor Data Sheets*, Intel Corp.

# AGP BUS Overview

The Accelerated Graphics Port (AGP) bus provides a very high speed bus interface between system logic and the high performance S3 Virge/ MX graphics accelerator in the Armada 7800 Family of Personal Computers. AGP provides a dedicated, point-to-point 66-MHz bus interface between the CPU Northbridge logic chip and the graphics accelerator. The AGP bus definition was developed as a superset to the 66-MHz PCI revision 2.1 specification, but was redefined to allow for only one device, the system graphics accelerator.

The AGP graphics implementation in the Compaq Armada 7800 Family of Personal Computers enables improved performance in 2D and 3D graphics applications as well as host-based video applications such as software-based MPEG and DVD playback. By moving the data transfers for these applications from the shared, 133-MB/s PCI bus to a dedicated, 266-MB/s AGP bus, the Armada 7800 architecture eliminates a significant bottleneck of previous portable system designs and enables new performance levels to be achieved.

# PCI B*u*s Ov*ervie*w

**NOTE:** This section describes the PCI bus in general and highlights bus implementation in this particular system. For detailed information regarding PCI bus operation, refer to the *PCI Local Bus Specification Revision 2.1*.

The standard PCI device configuration of the computer system has the processor/memory complex (via the CPU/PCI bridge) and the ISA bus (via the ISA/PCI bridge) connected to the PCI bus. PCI transactions occur synchronously with the host bus. The PCI bus operates at up to 33 MHz, providing 132-MB/s transfer performance. All I/O transactions involve the PCI bus. All ISA bus transactions with the microprocessor, cache memory, and/or system memory also involve the PCI bus. Memory transactions may or may not involve the PCI bus, depending on the source and destination.

#### PCI Bus Addressing

Four types of address cycles can take place on the PCI bus: I/O, memory, configuration, and special. Address decoding is distributed (left up to each device on the PCI bus).

Two types of address decoding are allowed on the PCI bus: positive and subtractive. Positive decoding provides higher performance because PCI devices respond immediately to an address within a certain range. For this system, most components on the PCI bus use positive decoding. Subtractive decoding is performed by the PCI/ISA bridge. A PCI device responds to its address by asserting the DEVSEL\_ signal. The PCI/ISA bridge decodes subtractively and asserts the DEVSEL\_ signal when no other PCI device responds to a cycle.

# I/O And Memory Cycles

For I/O addressing, a standard 32-bit address decode (AD31..0) for byte-level addressing is handled by the appropriate PCI device. For memory addressing, PCI devices decode the AD31..2 lines for DWORD-level addressing and check the AD1,0 lines for burst (linear incrementing) mode. In burst mode, subsequent data phases are conducted a DWORD at a time with addressing assumed to increment accordingly (4 bytes at a time).

Conf*igur*at*i*on Cycl*e*s

Devices on the PCI bus must comply with PCI protocol that allows configuration of that device by configuration software. In this system, Configuration Mechanism No.1 (as described in the *PCI Local Bus Specification Revision 2.1*) is employed. This method uses two 32-bit registers for initiating a configuration cycle for accessing the configuration space of a PCI device. The configuration address (CONFIG\_ADDRESS) register at IO address 0CF8h holds a value that specifies the PCI bus, PCI device, and specific register to be accessed. The configuration data (CONFIG\_DATA) register at IO address 0CFCh contains the configuration data.

#### Conf*igur*at*i*on Add*re*ss R*egi*st*er* I/O Po*r*t OC*F8*h, R/W

| BIT  | FUNCTION                                                                                   |

|------|--------------------------------------------------------------------------------------------|

| 31   | Configuration Enable<br>0 = Disabled<br>1 = Enabled                                        |

| 3024 | Reserved: read/write 0s.                                                                   |

| 2316 | Bus Number. Selects PCI bus to be used:<br>Read/Write 0's.                                 |

| 1511 | PCI Device Number. Selects PCI device to be accessed (refer to Table 3-1).                 |

| 108  | Function Number. Selects function of the PCI device.                                       |

| 72   | Register Index. Specifies configuration register to be accessed.                           |

| 1,0  | Config. Cycle Type ID:<br>00 = Type 0 (single PCI bus)<br>01 = Type 1 (multiple PCI buses) |

#### Conf*igur*at*i*on Data R*egi*st*er* I/O Po*r*t OC*F*Ch, R/W

| BIT | FUNCTION           |

|-----|--------------------|

| 310 | Configuration Data |

|     |                    |

The PCI device number determines which one of the AD31..11 lines is to be asserted high for the IDSEL function. These address lines act as a chip select for the PCI device to be configured. Table 3-1 lists the device numbers.

| Tabl <i>e 3-1</i><br>PCI D <i>e</i> v <i>i</i> c <i>e</i> N <i>u</i> mb <i>er</i> s |                                                              |                 |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------|

| PCI D <i>e</i> v <i>i</i> ce                                                        | PCI D <i>e</i> v <i>i</i> c <i>e</i> N <i>u</i> mb <i>er</i> | IDSEL Wired To: |

| CPU/PCI Bridge (MPC)                                                                | 0 (00h)                                                      | AD16            |

| ISA/PCI Bridge (MISC_L)                                                             | 14 (0Fh)                                                     | AD30            |

| Graphics Controller                                                                 | 13 (0Dh)                                                     | AD29            |

| PC Card Controller                                                                  | 12 (0Ch)                                                     | AD28            |

The computer system in the standard system configuration contains only one PCI bus, so that the configuration cycle type bits (<1,0>) of CF8h will be "00" to initiate a Type 0 configuration cycle.

The function number is used to select a particular function within a multifunction PCI device.

The register index identifies the 32-bit location within the configuration space of the PCI device to be accessed. All PCI devices can contain up to 256 bytes of configuration data of which the first 64 bytes (00h-3Fh) comprises a predefined configuration space header. The remaining 192 bytes (40h - FFh) are optional and device specific.

The PCI components are typically configured during POST. Each PCI device is identified with a vendor ID (allocated by the PCI Special Interest Group) and a device ID (allocated by the vendor).

# Sp*e*c*i*al Cycl*e*s

Special cycles are similar to configuration cycles and are initiated by writing to CONFIG\_ADDRESS (CF8h, Bus No. all 0s, Device = all 1s, Function = all 1s, and Register = all 0s) and CONFIG\_DATA (CFCh) to generate a Type 0 configuration cycle (Figure 3-6). This Type 0 cycle, however, does not assert any of the IDSEL lines and therefore results in a master abort with FFFFh returned to the microprocessor.

#### Option ROM Mapping

During POST, the PCI bus is scanned for devices that contain option ROM. The scan procedure follows the standard PC BIOS scan procedure. Beginning at C000h, memory is probed at intervals of 2-KB for the signature 0x55h at offset 0, and 0xAAh in location offset 1. This search terminates at E800h (F000h - 2KB).

Option ROMs have the following header format:

| Offs <i>e</i> t | Val <i>ue</i> | D <i>e</i> sc <i>ri</i> pt <i>i</i> on                            |

|-----------------|---------------|-------------------------------------------------------------------|

| 00h             | 55h           | First signature byte                                              |

| 01h             | AAh           | Second signature byte                                             |

| 02h             | Size          | Size of ROM modulo 512 (must round up to next 2K boundary)        |

| 03h             | Entry         | Start of installation subroutine (routine must have a far return) |

The size of the ROM in bytes is divided modulo 512 and rounded up to the next 2K boundary. For example, a 47K video ROM would have to be rounded up to 48K and divided modulo 512 to produce a value of 96 (60h).

When the BIOS finds the ROM signature, it will add the bytes modulo 256 starting at offset 00h, and will produce an error message if the sum isn't zero. Otherwise it will make a far call to the entry point at offset 3, then continue searching for ROMs on the next 2K boundary.

Option ROM data, if detected, is loaded into system memory's DOS compatibility area (C8000h-DFFFFh). In the standard configuration, only the video subsystem is detected as having option ROM (32K) and is loaded into RAM starting at C0000h.

#### ISA Bus Overview

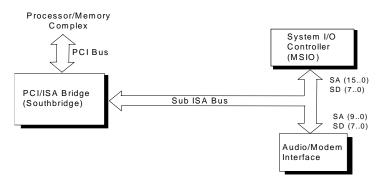

The ISA bus provides an 8-bit path for standard I/O peripherals as well as for optional devices that can be attached to the MultiBay Connector. Figure 3-3 shows the key functions and devices that reside on the ISA bus.

Figure 3-3. ISA Bus Block Diagram

Devices limited to 8-bit transfers use data lines SD<7..0> and the following control lines:

- MRDC\_ (memory read cycle low)

- MWTC\_ (memory write cycle low)

- SBHE\_ (byte high enable, accesses high byte)

- SA0\_ (accesses low byte)

- IORC\_ input/output read cycle low)

- IOWC\_ (input/output write cycle low, to enable or latch data on the data bus)

# Direct Memory Access

Direct memory access (DMA) is a method by which an ISA device accesses memory without involving the microprocessor. DMA reduces the amount of CPU interactions with memory, freeing the CPU for other processing tasks. DMA is normally used to transfer blocks of data to or from an ISA I/O device, but by implementation of Distributed DMA (DDMA) architecture, DMA devices are also allowed to exist on the PCI bus. The distributed DMA architecture is discussed later in the subsection "Distributed DMA."

The PCI/ISA bridge component includes the equivalent of two 8237 DMA controllers. The DMA circuitry is register-compatible with software written for AT-type systems.

Table 3-2 lists the default configuration of the DMA channels.

| Tabl <i>e 3-2</i><br>D <i>e</i> fa <i>u</i> lt DMA Chann <i>e</i> l Ass <i>ig</i> nm <i>e</i> nts |                                                                                                     |  |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

| DMA Chann <i>e</i> l                                                                              | <i>Fu</i> nct <i>i</i> on                                                                           |  |

| Cntlr 1 - Byte Transfers:                                                                         |                                                                                                     |  |

| 0                                                                                                 | Audio Controller                                                                                    |  |

| 1 (Default)                                                                                       | Audio Controller                                                                                    |  |

| 2                                                                                                 | Diskette Drive                                                                                      |  |

| 3                                                                                                 | EPP Parallel Port                                                                                   |  |

| Cntlr 2 - Word Transfers:                                                                         |                                                                                                     |  |

| 4 (0)                                                                                             | Cascade from Controller 1                                                                           |  |

| 5 (1)                                                                                             | Fast Infrared (8-bit Mode) EISA Ext.                                                                |  |

| 6 (2)                                                                                             | Spare                                                                                               |  |

| 7 (3)                                                                                             | Spare                                                                                               |  |

| NOTE: 1. Speakerphone use<br>2. Channel numbers                                                   | s one audio channel f <b>o</b> r and the other for Rx.<br>in parentheses are chann <b>els</b> MISC. |  |

All channels in Controller 1 (channels 0, 1, 2, and 3) operate at a higher priority than those in Controller 2 (channels 5, 6, and 7). Channel 4 of Controller 2 is not available for normal DMA. Unlike the CPU, DMA Controller 2 can transfer words only on an even address boundary. The DMA controller and page register define a 24-bit address that allows data transfers within the address space of the CPU. The DMA controllers operate at 8 MHz.

. . . . . . . . . . . . . . .

## DMA Memory Page Register

The DMA memory page register contains the 8 most-significant bits of the 24-bit address. It works in conjunction with the DMA controllers to define the complete (24-bit) address for the DMA channels. Table 3-3 gives the port address assigned to each page register.

| Tabl <i>e 3-3</i><br>DMA Po <i>r</i> t Add <i>re</i> ss <i>e</i> s |                                |  |

|--------------------------------------------------------------------|--------------------------------|--|

| DMA Channel                                                        | Page Register I/O Port Address |  |

| 0                                                                  | 087h                           |  |

| 1                                                                  | 083h                           |  |

| 2                                                                  | 081h                           |  |

| 3                                                                  | 082h                           |  |

| 4                                                                  | None                           |  |

| 5                                                                  | 08Bh                           |  |

| 6                                                                  | 089h                           |  |

| 7                                                                  | 08Ah                           |  |

| Refresh                                                            | 08Fh (See Note)                |  |

**NOTE:** The DMA memory page register for the refresh channel must be programmed with 00h for proper system operation.

The memory address is derived as follows:

24-Bit Address - Controller 1 (Byte Transfers)

| 8-bit Page Register | 8-Bit DMA Controller |

|---------------------|----------------------|

| A23A16              | A15A0                |

24-Bit Address - Controller 2 (Word Transfers)

| 7-bit Page Register | 16-Bit DMA Controller |

|---------------------|-----------------------|

| A23A17              | A16A1, A0 always 0    |

A16 from the DMA Memory Page register is disabled when DMA Controller 2 is selected. A0 is not connected to DMA Controller 2 and is always 0 when word-length transfers are selected. Not connecting A0 means that the size of the block of data that can be moved or addressed is measured in 16-bit words, rather than 8-bit bytes, and the words must always be on an even boundary.

DMA Controller 1 can move as much as 64 KBs of data per DMA transfer. DMA Controller 2 can move as much as 64K words, or 128 KB of data per DMA transfer. Word DMA operations are only possible between 16-bit memory and 16-bit peripherals.

#### D*i*st*ri*b*u*t*e*d DMA

The distributed DMA architecture provided by the PCI/ISA bus bridge device allows the individual DMA controller channels to be distributed between all PCI devices as well as ISA bus devices. The I/O address space for each channel is separated into a consecutive 16-byte block, which is then mapped, relative to a base address, into the 64-KB I/O address space. A new distributed master DMA interface ties the old and new I/O registers together and will control all reads and writes to any legacy DMA I/O register.

The DDMA registers are defaulted to I/O memory space 0800h - 087Fh. The base address for these registers are programmed in the system unit PCI/ISA bridge device and are programmable to be any contiguous 128-byte block on even boundaries, i.e., 0, 80, 100, 180. The DDMA registers are distributed throughout the system according to the DMA channel used by the individual PCI device.

The PCI/ISA bus bridge device can be configured to be a master DMA by setting bit 31 in the PCI distributed DMA configuration register. When the PCI/ISA bus bridge device is enabled as a master DMA controller it will monitor all PCI I/O reads and writes to all Legacy DMA registers. Both the system PCI/ISA bus bridge device and the expansion base PCI/ISA bus bridge device use all seven DMA channels. It is up to the software to ensure that the same DMA channels are not enabled in both PCI/ISA bus bridge devices.

The monitored cycles are controlled as shown in the following list:

- 1. A PCI I/O cycle is initiated on the PCI bus with a legacy DMA when a read/write to a Legacy DMA register is attempted by the CPU bridge device. The master DMA uses the "Retry Engine" and takes control of the cycle by driving DEVSEL\_ to request the PCI bus and issues a "retry" to terminate the cycle after IRDY is activated.

- 2. The request by the CPU bridge device is then immediately masked by the PCI arbiter.

- 3. The master DMA runs up to seven PCI I/O byte reads/writes after being granted the PCI bus. PCI bus multibyte access is serviced to completion one byte at a time.

- 4. The master DMA will set an internal completion flag at the end of the first read/write cycle, the request CPU pin is unmasked, and the master DMA interface relinquishes control of the PCI bus. The master DMA waits for the retried PCI I/O read/write from the CPU bridge device.

- 5. Access to Legacy DMA Registers from sources other than the host bridge device will be serviced normally by the master DMA. The PCI I/O read/write cycle is reinitiated and the data is returned by the master DMA for a read. For a write that is initiated after IRDY is activated, the cycle is terminated and will reset the internal flag.

The DMA Master Configuration Register is described as follows:

Address: 08Ch-08Fh, R/W, Reset Value: 0000000h

| BIT | RUNCTION                                                                                                                                                                                                            |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31  | Master DMA enabled<br>0 = Disabled<br>1 = Enabled                                                                                                                                                                   |

| 308 | Reserved - read/write 0s.                                                                                                                                                                                           |

| 75  | Identifies active DMA channel in PCI/ISA bridge device. One bit per channel.<br>0 = Distributed Legacy DMA Channel<br>1 = Local Legacy DMA Channel                                                                  |

| 4   | Reserved - read/write 0s.                                                                                                                                                                                           |

| 3-0 | $\begin{array}{l} \mbox{Identifies active DMA channel in PCI/ISA bridge device} \ . \ One \ bit \ per \ channel. \\ 0 = \ Distributed \ Legacy \ DMA \ Channel \\ 1 = \ Local \ Legacy \ DMA \ Channel \end{array}$ |

**NOTE:** Bits 0-3 and 5-7 are tied to their corresponding DMA Slave Configuration Register. Therefore, a write or read from either location will automatically be reflected in the other register on read.

### Refresh Operations

The RAM refresh is designed to perform a memory read cycle on each of the 512 row addresses in the DRAM memory space. Refresh operations are used to refresh memory on the 64-bit memory bus. The remaining address lines are in an undefined state during the refresh cycle. Hidden refresh of the DRAM is performed in the system while refresh timing on the ISA bus of the expansion base is set by the Refresh Count Value Register in the PCI configuration space of the MISC-E device.

#### Int*erru*pts

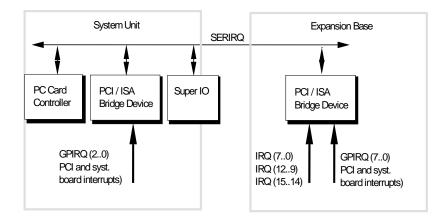

The Interrupts used in the Armada 7800 Family of Personal Computers are serialized as shown in Figure 3-4. The PCI and ISA interrupts are routed to the PCI/ISA bridge device on the expansion base, where they are serialized onto a single wire bus to the PCI/ISA bridge device in the system unit. They are then MUXed with the system unit IRQs and fed to the interrupt controller.

Figure 3-4. SER IRQ Serial Interrupt Bus Architecture, Block Diagram

The GPIRQ pins are mapped by the same mapping logic in both the system unit and expansion base PCI/ISA bridge devices to any ISA IRQ with the exception of IRQ0, IRQ1, IRQ2, IRQ8, and IRQ13. The mapped IRQs, standard IRQ pins, and internal interrupts are ANDed by both PCI/ISA bridge devices. The data is then serialized and placed on the serial bus. The output of the serial bus is sent by the system unit PCI/ISA bridge device to the Edge/Level Control registers and then to the 8259 interrupt controllers.

For further information concerning Serialized Interrupts, refer to the joint publication by Compaq and other companies titled *Serialized IRQ on the "PCI Way"* Version 5.4.

The Interrupt Index Register and Mapping Registers are described as follows:

#### Int*erru*pt Ind*e*x R*egi*st*er* Add*re*ss: AEh, R/W, R*e*s*e*t Val*ue*: 0000h

| BIT | FUNCTION                                                                          |  |  |

|-----|-----------------------------------------------------------------------------------|--|--|

| 73  | Reserved - read/write 0s.                                                         |  |  |

| 20  | GP_IRQ Index. Specifies GPIRQ pins for mapping in the Interrupt Mapping Register. |  |  |

|     | GPIRQ 3 & 4 are IDE interrupts. Only index values 0-5 are valid.                  |  |  |

|     | 000 = GPIRQ 0 011 = GPIRQ 5 (Expansion PCI/ISA bridge device only)                |  |  |

|     | 001 = GPIRQ 1 100 = GPIRQ 6 (Expansion PCI/ISA bridge device only                 |  |  |

|     | 010 = GPIRQ 2 101 = GPIRQ 7 (Expansion PCI/ISA bridge device only)                |  |  |

#### Int*erru*pt Mapp*i*n*g* R*egi*st*er* Add*re*ss: A*F*h, R/W, R*e*s*e*t Val*ue*: 01h

| BIT | FUNCTION                                                                                                                                                 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 74  | Interrupt Map Value represents which IREQ controller is mapped by the GP_IRQ in the Interrupt Index Register. Interrupts 0.1, 2, 8, and 13 are reserved. |

| 31  | Reserved - read/write 0s.                                                                                                                                |

| 0   | Interrupt Disable<br>1 - The selected interrupt is disabled<br>0 - The selected interrupt is enabled                                                     |

The Interrupt Edge Level Control Register is described as follows:

#### Ed*ge* Level Control Register Address:04D0h, R/W, Reset Value: 0000h

| BIT  | FUNCTION                                                    |

|------|-------------------------------------------------------------|

| 1514 | INT 15/INT 14 Level Mode<br>0 = Edge Mode<br>1 = Level Mode |

| 13   | Reserved - read/write 0s.                                   |

| 129  | INT 12/INT 9 Level Mode<br>0 = Edge Mode<br>1 = Level Mode  |

| 8    | Reserved - read/write 0s.                                   |

| 73   | INT 7/INT 3 Level Mode<br>0 = Edge Mode<br>1 = Level Mode   |

| 20   | Reserved - read/write 0s.                                   |

# Nonmaskable Interrupts

The microprocessor uses two basic types of interrupts: maskable and nonmaskable. A nonmaskable interrupt cannot be masked off within the processor, but may be masked under software control using additional logic on the system board. A maskable interrupt can be enabled or disabled by the microprocessor using the STI and CLI instructions.

There are two interrupt signals that are nonmaskable by the microprocessor: the SMI\_ and NMI signals. The SMI\_ signal is used for power management and is discussed in Appendix B, "Power Conservation." This section describes the NMI signal. An NMI signal is caused by:

- Parity errors on any expansion boards that pull the IOCHK\_ line low

- Parity errors detected on the PCI bus including Special Cycles

- Parity errors detected on the PCI bus (except Special Cycles)

When an NMI is caused by hardware, register 61h indicates the source of the interrupt. Bits set to 1 in port 61h show which device requested an NMI. After the NMI routine processes the interrupt, the NMI status bits [7, 6] are reset.

If bit [6] is set, the interrupt comes from the hardware IOCHK\_ line. To reset the hardware IOCHK\_ latch, pulse bit [3] of port 61h high.

If bit [7] is set, the interrupt comes from a processor board parity error. To reset the parity error latch bit, pulse bit [2] of port 61h high.

The registers that affect NMI generation are described in the following paragraphs.

# NMI Status Register

This register provides various functions including those related to the NMI. Note that bits 7..4 are meant as read-only bits.

#### NMI Status Register Address: 061h

| BIT | FUNCTION                                                                                                                             |

|-----|--------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SERR_NMI Source Status: R0<br>0 = No NMI from system board parity error<br>1 = NMI requested                                         |

| 6   | IOCHK_ NMI Source Status: R0<br>0 = No NMI from IOCHK_<br>1 = IOCHK_ is low (active), NMI requested, read<br>only                    |

| 5   | Timer Counter 2 OUT Status: RO<br>State of the interval timer<br>1, counter 2 output signal (speaker), read only                     |

| 4   | Refresh Cycle Toggle: RO<br>This bit toggles with every refresh.                                                                     |

| 3   | IOCHK_ NMI Enable: R0<br>0 = IOCHK_ NMI enabled<br>1 = IOCHK_ NMI disabled and cleared, read and<br>write                            |

| 2   | System Board PCI SERR#NMI Enable: RW<br>0 = Parity error NMI enabled<br>1 = Parity error NMI disabled and cleared, read<br>and write |

| 1   | Speaker Data Enable: RW<br>0 = SPKR output is 0<br>1 = SPKR output is the value of Counter 2 OUT                                     |

| 0   | Timer Counter 2 Enable: RW<br>Gate signal for interval timer, counter 2 (speaker)<br>0 = Counter 2 disabled<br>1 = Counter 2 enabled |

# NMI Enable Register

The Mask register for the NMI interrupt is at I/O address 70h shown below. Writing 80h to this port masks the NMI from all sources. Note that if the NMI is masked, the non-maskable interrupt from the NMI port, the Bus Master Timeout, and the Fail-Safe Timer will not be generated and the appropriate bits in register 061h will not be set. Even if NMI is masked, the proper bits for the IOCHK\_ and parity error bits in register 061h will be set. If NMI is not masked and these bits are set, then NMI will be generated at that time.

This port is shared with the real-time clock and configuration memory device (the lower 7 bits). Do not modify the contents of this register without considering the effects on the state of the other bits. Refer to the "Real-Time Clock and Configuration Memory" subsection on the usage of I/O address 70h for time and system information.

NMI Enable Register Address: 070h

| BIT | FUNCTION         |

|-----|------------------|

| 7   | 0 = NMI enabled  |

|     | 1 = NMI disabled |

| 60  | Real-time clock  |

# Maskable Interrupts

All maskable (hardware) interrupts generated by PCI and ISA peripherals are channeled through 8259-type interrupt control logic that is integrated into the PCI/ISA bridge device. PCI interrupts are applied to the PCI interrupt redirect logic. The redirect logic maps the PCI interrupts to selected ISA (IRQ) interrupts. The IRQn interrupts are then processed as in standard AT-type systems, with the microprocessor responding to the active INTR signal.

The maskable interrupt logic is register-compatible with software written for standard AT-type systems.

Table 3-4 lists the 15 possible sources for maskable interrupts and their priorities. The highest-priority interrupt is processed first.

| P <i>ri</i> o <i>ri</i> ty | Lab <i>e</i> l | Cont <i>r</i> oll <i>er</i> | Typ <i>i</i> cal Int <i>erru</i> pt So <i>ur</i> c <i>e</i>            |

|----------------------------|----------------|-----------------------------|------------------------------------------------------------------------|

| 1                          | IRQO           | 1                           | Interval timer 1, counter 0 output (System Timer)**                    |

| 2                          | IRQ1           | 1                           | Keyboard Controller                                                    |

| 3                          | IRQ8           | 2                           | Real-time clock (RTC)                                                  |

| ļ                          | IRQ9           | 2                           | Expansion Bus pin B04*                                                 |

| 5                          | IRQ10          | 2                           | Expansion Bus pin B03*                                                 |

| 6                          | IRQ11          | 2                           | Expansion Bus pin D04*                                                 |

| 7                          | IRQ12          | 2                           | Mouse Controller/Expansion Bus pin D05*                                |

| 3                          | IRQ13          | 2                           | Coprocessor error**                                                    |

| )                          | IRQ14          | 2                           | IDE Controller /Expansion Bus pin D07*                                 |

| 0                          | IRQ15          | 2                           | Expansion Bus pin D06* Secondary IDE Controller                        |

| 1                          | IRQ3           | 1                           | Serial (infrared) port 1(COM2)/<br>Expansion Bus pin B25* (Modem Only) |

| 2                          | IRQ4           | 1                           | Shared Serial (RS-232) port 2 (COM3)<br>(COM1)/Expansion Bus pin B24*  |

| 3                          | IRQ5           | 1                           | Parallel Port 2/Expansion Bus pin B23* (Audio)                         |

| 4                          | IRQ6           | 1                           | Diskette drive controller/Expansion Bus pin B22*                       |

| i                          | IRQ7           | 1                           | Parallel Port 1/Expansion Bus pin B21*                                 |

|                            | IRQ2           | 1                           | Interrupt from Controller 2 (cascaded)                                 |

\*\*System Unit PCI/ICS bridge device (internal).

The Numeric Coprocessor Interrupt is created by synchronizing FERR with PCICLK to generate IRQ13.

Int*er*val T*i*mer

The purpose of a programmable interval timer is to generate pulses at software controllable intervals. This system uses one 8254-compatible timer in the PCI/ISA bridge device that provides three counters. Table 3-5 lists the interval timer functions.

| Tabl <i>e 3-5</i><br>Int <i>er</i> val T <i>i</i> m <i>er Fu</i> nct <i>i</i> ons |                           |                  |           |                    |

|-----------------------------------------------------------------------------------|---------------------------|------------------|-----------|--------------------|

| Co <i>u</i> nt <i>er</i>                                                          | <i>Fu</i> nct <i>i</i> on | Gat <i>e</i>     | Clock In  | Clock O <i>u</i> t |

| 0                                                                                 | System Clock              | Always On        | 1,193 MHz | IRQO               |

| 1                                                                                 | Not Used                  | N/A              | N/A       | N/A                |

| 2                                                                                 | Speaker Tone              | Port 61, bit [0] | 1,193 MHz | Speaker Input      |

Counter 0 provides a system interrupt for the time of day, diskette timeout, and other system functions. Counter 2 generates the tone for the "beep" speaker. The output to the speaker is enabled by ANDing it (SPKCLK) with Port 61h bit [1]. The output of the counter can be read at Port 61h bit [5] (regardless of enable bit [0] status). See the Port 61h bit descriptions under "Nonmaskable Interrupts" in this chapter for more information. To minimize power dissipation in the speaker, the speaker output should be left high (port 61h, bit [1] set to 1) when not in use.

The facilities available for programming the timers include:

- Control Word specifies:

- $\Box$  which counter to read or write.

- $\Box$  the operating mode.

- □ the count format (binary or BCD).

- Counter Latch latches the current count so that it can be read by the system; the countdown process continues.

- Read Back reads the count value, programmed mode, the current state of the OUT pins, and the state of the Null Count Flag of the selected counter.

| Tabl <i>e 3-6</i><br>Int <i>er</i> val T <i>i</i> m <i>er</i> Po <i>r</i> t <i>Fu</i> nct <i>i</i> ons |                                                     |  |  |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|

| Po <i>r</i> t                                                                                          | <i>Fu</i> nct <i>i</i> on                           |  |  |

| 40h                                                                                                    | Read or Write count for counter 0 (system clock)    |  |  |

| 41h                                                                                                    | Read or Write count for counter 1 (refresh request) |  |  |

| 42h                                                                                                    | Read or Write count for counter 2 (speaker tone)    |  |  |

| 43h                                                                                                    | Control Word Register                               |  |  |

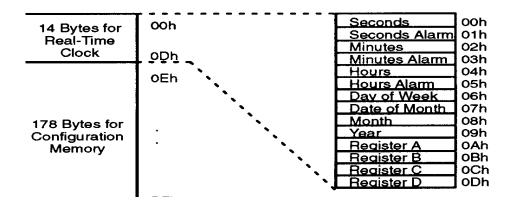

# Real-Time Clock and Configuration Memory

The real-time clock (RTC) is compatible with the MC146818 device. The auxiliary battery is used to provide power to the RTC and the configuration data stored in EEPROM. When fully charged and all other power sources are disconnected, the date and time are held for at least one month.

The first 14 memory locations of configuration memory are used for the RTC. The remaining memory locations are used for system configuration.

All registers are read/write except:

- Status registers C and D, which are read only.

- Bit[7] of status register A, which is read only.

- The high-order bit of the seconds byte, which is read only.

Figure 3-5 shows the memory map for the real-time clock.

#### Figure 3-5. RTC/Configuration Memory Map

To reset the time or system configuration, run the Compaq SETUP Utility or use the appropriate INT 1Ah (BIOS) command. The TIME and DATE commands of DOS 3.31 or the date/time properties window of Windows 95 also update the RTC.

The RTC is an I/O-mapped device using indirection (see below).

To write a value into configuration memory:

- 1. Use OUT 70h, AL to specify the memory location to change. 70h is the port number; AL is the memory location.

- 2. Use OUT 71h, AL to specify the data for the memory location. 71h is the port number; AL is the data.

To read the contents of a memory location:

- 1. Use OUT 70h, AL to specify the memory location to read. 70h is the port number; AL is the memory location.

- 2. Use IN AL, 71h to read the data stored in that location. The returned data is placed in the AL register of the processor.

The port 70h is shared between the NMI Mask register and the Configuration Memory Address register. To leave the NMI Mask enabled, write a "0" to bit [7] of the RTC address

Table 3-7 summarizes the types of information stored in the RTC and Configuration memory locations.

| Tabl <i>e 3-7</i><br>R <i>e</i> al-T <i>i</i> m <i>e</i> Clock and Conf <i>igur</i> at <i>i</i> on M <i>e</i> mo <i>r</i> y Locat <i>i</i> ons |                           |                           |                                         |  |